# int<sub>el</sub>.

# Intel<sup>®</sup> 82801EB (ICH5) I/O 82801ER (ICH5R), and 82801DB (ICH4) Controller Hub: AC '97 PRM

**Programmers Reference Manual (PRM)**

April 2003

Document Number: 252751-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 82801EB (ICH5) I/O 82801ER (ICH5R), and 82801DB (ICH4) controller hub may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2$ C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2$ C bus/protocol and was developed by Intel. Implementations of the  $l^2$ C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2003, Intel Corporation

# int<sub>el</sub>,

# **Contents**

| 1 | Introd             | uction                |                                                                      | 7  |

|---|--------------------|-----------------------|----------------------------------------------------------------------|----|

|   | 1.1                | About T               | his Document                                                         | 7  |

|   | 1.2                | Referen               | ce Documents and Information Sources                                 | 9  |

| 2 | Overv              | iew                   |                                                                      | 11 |

|   | 2.1                | Intel <sup>®</sup> IC | H5 AC '97 Controller Compatibility                                   | 11 |

|   | 2.1                | 2.1.1                 | Third AC '97 Component Specification Revision 2.1, Revision 2.2 an   |    |

|   |                    |                       | Revision 2.3 Compliant Codecs                                        | 14 |

|   |                    | 2.1.2                 | Dedicated S/P DIF DMA Output Channel                                 |    |

|   |                    | 2.1.3                 | 20 Bits Surround PCM Output                                          |    |

|   |                    | 2.1.4                 | Memory Map Status and Control Registers                              |    |

|   |                    | 2.1.5                 | Second Independent Input DMA Engines                                 |    |

|   | 2.2                | 2.1.6                 | PCI Local Bus Specification, Revision 2.3 Power Management           |    |

|   | 2.2                | General               | Requirements                                                         | 10 |

| 3 | Intel <sup>®</sup> | ICH5 AC '             | 97 Controller Theory of Operation                                    | 17 |

|   | 3.1                | Intel <sup>®</sup> IC | H5 AC '97 Initialization                                             | 17 |

|   |                    | 3.1.1                 | System Reset                                                         | 17 |

|   |                    | 3.1.2                 | Codec Topology                                                       | 17 |

|   |                    | 3.1.3                 | BIOS PCI Configuration                                               |    |

|   |                    | 3.1.4                 | Hardware Interrupt Routing                                           |    |

|   |                    | 3.1.5                 | PCI Lock                                                             |    |

|   | 3.2                |                       | ngines                                                               |    |

|   |                    | 3.2.1                 | Buffer Descriptor List                                               |    |

|   |                    | 3.2.2                 | DMA Initialization                                                   |    |

|   |                    | 3.2.3                 | DMA Steady State Operation                                           |    |

|   |                    | 3.2.4                 | Stopping Transfers                                                   |    |

|   |                    | 3.2.5                 | FIFO Error Conditions                                                |    |

|   |                    |                       | 3.2.5.1         FIFO Underrun           3.2.5.2         FIFO Overrun |    |

|   | 3.3                | Channa                | I Arbitration                                                        |    |

|   |                    |                       |                                                                      |    |

|   | 3.4                | 3.4.1                 | ffers                                                                |    |

|   |                    | •••••                 | Memory Organization of Data<br>PCM Buffer Restrictions               |    |

|   |                    | 3.4.2<br>3.4.3        | FIFO Organization                                                    |    |

|   | 3.5                |                       | Codec/Driver Support                                                 |    |

|   | 5.5                | 3.5.1                 | Codec Register Shadowing                                             |    |

|   |                    | 3.5.2                 | Codec Access Synchronization.                                        | 20 |

|   |                    | 3.5.3                 | Data Request Synchronization in Audio Split Configurations           |    |

|   | 3.6                |                       | Aanagement                                                           |    |

|   | 0.0                | 3.6.1                 | Codec Topologies                                                     |    |

|   |                    | 0.0.1                 | 3.6.1.1 Tertiary Codec Topologies                                    |    |

|   |                    | 3.6.2                 | Power Management Transition Maps                                     |    |

|   |                    | 3.6.3                 | Power Management Topology Considerations                             |    |

|   |                    |                       | - 0                                                                  |    |

|   |                      |             | 3.6.3.1     | Determining the Presence of Secondary and Tertiary Codecs. | 34 |

|---|----------------------|-------------|-------------|------------------------------------------------------------|----|

|   |                      |             | 3.6.3.2     | Determining the Presence of a Modem Function               | 35 |

|   |                      | 3.6.4       |             | Context Recovery                                           |    |

|   |                      | 3.6.5       |             | e Power Management                                         |    |

|   |                      |             | 3.6.5.1     | Primary Audio Requested to D3                              | 36 |

|   |                      |             | 3.6.5.2     | Secondary Modem Requested to D3                            |    |

|   |                      |             | 3.6.5.3     | Secondary Modem Requested to D0                            | 36 |

|   |                      |             | 3.6.5.4     | Audio Primary Requested to D0                              |    |

|   |                      |             | 3.6.5.5     | Using a Cold or Warm Reset                                 | 37 |

| 4 | Surrou               | nd Audio S  | Support     |                                                            | 39 |

|   | 4.1                  | Determin    | e Codec's   | Audio Channels                                             | 39 |

|   | 4.2                  |             |             | 5 AC '97 Controller Audio Channels                         |    |

| 5 | 20-Bits              | PCM Sup     | port        |                                                            | 43 |

| 6 | Indepe               | ndent S-P   | /DIF Outpu  | It Capability                                              | 45 |

| 7 | Suppor               | rt for Doub | le Rate Au  | dio                                                        | 47 |

| 8 | Indepe               | ndent Inpu  | ut Channels | s Capability                                               | 49 |

|   | 8.1                  | Link Top    | ology Deter | rmination                                                  | 49 |

| 9 | Intel <sup>®</sup> I | CH5 AC '9   | 7 Modem I   | Driver                                                     | 51 |

|   | 9.1                  | Robust H    | lost-Based  | Generation of a Synchronous Data Stream                    | 51 |

|   |                      | 9.1.1       |             | Data Algorithm                                             |    |

|   |                      | 9.1.2       |             | 5 AC '97 Spurious Data Implementation                      |    |

# int<sub>el</sub>,

# Figures

| Figure 1. Block Diagram of Platform Chipset with Intel <sup>®</sup> ICH5 Component     | . 13 |

|----------------------------------------------------------------------------------------|------|

| Figure 2. Intel <sup>®</sup> ICH5 AC '97 Controller Connection to Its Companion Codecs | . 14 |

| Figure 3. Generic Form of Buffer Descriptor (One Entry in the List)                    | . 20 |

| Figure 4. Buffer Descriptor List                                                       | . 21 |

| Figure 5. Compatible Implementation with Left and Right Sample Pair in Slot 3/4 Every  | ,    |

| Frame                                                                                  | . 26 |

| Figure 6. Compatible Implementation with Sample Rate Conversion Slots 3 and 4          |      |

| Alternating over Next Frame                                                            | . 26 |

| Figure 7. Incompatible Implementation of Sample Rate Conversion with Repeating Slot    | ts   |

| over Next Frames                                                                       | . 27 |

|                                                                                        |      |

# **Tables**

| Table 1. Applicable Components                                               | 7  |

|------------------------------------------------------------------------------|----|

| Table 2. Audio Features Distribution Matrix                                  |    |

| Table 3. Audio Registers                                                     | 18 |

| Table 4. Modem Registers                                                     | 19 |

| Table 5. BD Buffer Pointer (DWORD 0: 00-03h)                                 | 20 |

| Table 6. BD Control and Length (DWORD 1: 04-07h)                             | 21 |

| Table 7. Audio Descriptor List Base Address                                  |    |

| Table 8. Modem Descriptor List Base Address                                  | 22 |

| Table 9. Audio Last Valid Index                                              | 22 |

| Table 10. Modem Last Valid Index                                             | 23 |

| Table 11. FIFO Summary                                                       | 27 |

| Table 12. SDM Register Description                                           | 28 |

| Table 13. Dual Codecs Topologies                                             | 30 |

| Table 14. Power State Mapping for Audio Single or Dual (Split) Codec Desktop |    |

| Transition                                                                   |    |

| Table 15. Power State Mapping for Modem Single Codec Desktop Transition      |    |

| Table 16. Power State Mapping for Audio in Dual Codec Desktop Transition     |    |

| Table 17. Power State Mapping for Modem in Dual Codec Desktop Transition     |    |

| Table 18. Extended Audio ID Register                                         |    |

| Table 19. Single Codec Audio Channel Distribution                            | 39 |

| Table 20. Multiple Codec Audio Channel Distribution                          |    |

| Table 21. CM 4/6 – PCM Channels Capability Bits                              |    |

| Table 22. AC-Link PCM 4/6 -Channels Enable Bits                              |    |

| Table 23. Sample Capabilities                                                |    |

| Table 24. PCM Out Mode Selector                                              |    |

| Table 25. Global Control Register S-P/DIF Slot Map Bits                      |    |

| Table 26. Topology Descriptor                                                |    |

| Table 27. SDATA_IN Map                                                       |    |

| Table 28. Codec Ready Bits                                                   |    |

| Table 29. MMBAR: Mixer Base Address Register                                 | 50 |

# **Revision History**

| Revision<br>Number | Description      | Revision Date |

|--------------------|------------------|---------------|

| -001               | Initial Release. | April 2003    |

# 1 Introduction

# 1.1 About This Document

This document was prepared to assist Independent Hardware and Software Vendors (IHVs and ISVs) in supporting the Intel<sup>®</sup> I/O controller hub (ICH5) AC '97 controller feature set. This document also applies to the previous generation of Intel I/O controller hub components and describes the general requirements to develop an audio driver that will make use of the AC '97 audio interface.

This document also describes functions that the BIOS or Operating Systems (OS) must perform in order to ensure correct and reliable operation of the platform. This document will be supplemented from time to time with specification updates. The specification updates contain information relating to the latest programming changes. Check with your Intel representative for availability of specification updates.

The following table outlines ICH device information at a glance.

| Device Name               | Vendor ID | Device ID | Subsystem Vendor<br>ID                                                            | Subsystem Device<br>ID                                                            | Base Class Code | Sub-Class Code | Prog. Interface | Revision ID | Bus Number (PCI<br>Addr) | Device Number | Function Number | Microsoft PNP<br>Device Node ID                                                         | Intel Desired Device<br>Description (INF<br>name) Name for:<br>Microsoft Windows*<br>Operating System |

|---------------------------|-----------|-----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|----------------|-----------------|-------------|--------------------------|---------------|-----------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Intel <sup>®</sup><br>ICH | 8086      | 2415      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh           | 5               | PCI/VEN_8086&DE<br>V_2415 (subsystem<br>will also provide<br>additional<br>information) | Intel <sup>®</sup> 82801AA AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)      |

| Intel<br>ICH              | 8086      | 2416      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 07h             | 03h            | 00h             | ALL         | 00h                      | 1Fh           | 6               | PCI/VEN_8086&DE<br>V_2416 (subsystem<br>will also provide<br>additional<br>information) | Intel 82801AA AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF)                   |

| Intel<br>ICH-0            | 8086      | 2425      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh           | 5               | PCIIVEN_8086&DE<br>V_2425<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> 82801AB AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)      |

#### **Table 1. Applicable Components**

| Device Name                 | Vendor ID | Device ID | Subsystem Vendor<br>ID                                                            | Subsystem Device<br>ID                                                            | Base Class Code | Sub-Class Code | Prog. Interface | <b>Revision ID</b> | Bus Number (PCI<br>Addr) | <b>Device Number</b> | Function Number | Microsoft PNP<br>Device Node ID                                                         | Intel Desired Device<br>Description (INF<br>name) Name for:<br>Microsoft Windows*<br>Operating System                       |

|-----------------------------|-----------|-----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|----------------|-----------------|--------------------|--------------------------|----------------------|-----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Intel <sup>®</sup><br>ICH-0 | 8086      | 2426      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 07h             | 03h            | 00h             | ALL                | 00h                      | 1Fh                  | 6               | PCI/VEN_8086&DE<br>V_2426 (subsystem<br>will also provide<br>additional<br>information) | Intel 82801AB AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF)                                         |

| Intel <sup>®</sup><br>ICH2  | 8086      | 2435      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL                | 00h                      | 1Fh                  | 5               | PCI/VEN_8086&DE<br>V_2435 (subsystem<br>will also provide<br>additional<br>information) | Intel <sup>®</sup> "ICH2" AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                             |

| ICH2                        | 8086      | 2436      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL                | 00h                      | 1Fh                  | 6               | PCI/VEN_8086&DE<br>V_2436<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH2 DT/Server<br>/Mobile/Low End" AC<br>'97 Modem Controller<br>(displayed by driver<br>provider's INF) |

| Intel <sup>®</sup><br>ICH3  | 8086      | 2445      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL                | 00h                      | 1Fh                  | 5               | PCI/VEN_8086&DE<br>V_2445 (subsystem<br>will also provide<br>additional<br>information) | Intel <sup>®</sup> "ICH3" AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                             |

| ІСНЗ                        | 8086      | 2446      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL                | 00h                      | 1Fh                  | 6               | PCI/VEN_8086&DE<br>V_2446<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH3 DT/Server<br>/Mobile/Low End" AC<br>'97 Modem Controller<br>(displayed by driver<br>provider's INF) |

| Intel <sup>®</sup><br>ICH4  | 8086      | 24C5      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL                | 00h                      | 1Fh                  | 5               | PCIVEN_8086&DE<br>V_24C5<br>(subsystem will also<br>provide additional<br>information)  | Intel <sup>®</sup> "ICH4" AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                             |

| ICH4                        | 8086      | 24C6      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL                | 00h                      | 1Fh                  | 6               | PCI/VEN_8086&DE<br>V_24C6<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH4 DT/Server<br>/Mobile/Low End" AC<br>'97 Modem Controller<br>(displayed by driver<br>provider's INF) |

| Device Name                | Vendor ID | Device ID | Subsystem Vendor<br>ID                                                            | Subsystem Device<br>ID                                                            | Base Class Code | Sub-Class Code | Prog. Interface | Revision ID | Bus Number (PCI<br>Addr) | Device Number | Function Number | Microsoft PNP<br>Device Node ID                                                         | Intel Desired Device<br>Description (INF<br>name) Name for:<br>Microsoft Windows*<br>Operating System                 |

|----------------------------|-----------|-----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|----------------|-----------------|-------------|--------------------------|---------------|-----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Intel <sup>®</sup><br>ICH5 | 8086      | 24D5      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh           | 5               | PCI/VEN_8086&DE<br>V_24D5<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> "ICH5" AC '97<br>Audio Controller<br>(displayed by driver<br>provider's INF)                       |

| ICH5                       | 8086      | 24D6      | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | Default is 00h.<br>Value of this<br>register varies<br>according to the<br>system | 04h             | 01h            | 00h             | ALL         | 00h                      | 1Fh           | 6               | PCI/VEN_8086&DE<br>V_24D6<br>(subsystem will also<br>provide additional<br>information) | Intel <sup>®</sup> ICH5 DT/Server<br>/ Low End" AC '97<br>Modem Controller<br>(displayed by driver<br>provider's INF) |

#### **Reference Documents and Information Sources** 1.2

| Document Name or Information Source                                        | Available From                                         |

|----------------------------------------------------------------------------|--------------------------------------------------------|

| Audio Codec '97 Specification, Revision 2.1, Revision 2.2 and Revision 2.3 | http://www.intel.com/labs/media/audi<br>o/index.htm    |

| Communications and Networking Riser Specification, Version 1.0 and 1.2     | http://developer.intel.com/technology<br>/cnr/         |

| PCI Local Bus Specification, Revision 2.3                                  | http://www.pcisig.com/specifications/<br>conventional/ |

| Microsoft Windows* Driver Development Kits                                 | Microsoft                                              |

| - http://www.microsoft.com/ddk                                             |                                                        |

| Microsoft Windows* Driver and Hardware Development                         | Microsoft                                              |

| http://www.microsoft.com/hwdev                                             |                                                        |

**NOTE:** 1. Contact your Intel representative for the current document revision.

This page is intentionally left blank.

# 2 Overview

In this document, "ICH5" stands for I/O Controller Hub 5. The ICH5 provides an AC '97compliant controller. References to the "AC '97 Component Specification" refer to the *Audio Codec '97 Specification*, Revision 2.1, Revision 2.2, and Revision 2.3. The ICH5 AC '97 Digital Controller implementation interfaces to AC '97 Component Specification, Revision 2.3 and below-compliant codecs. The ICH5 supports up to three AC '97 Component Specification compliant codecs on the AC-link interface.

This document is limited to specifying the software requirements and driver interface for the ICH5 AC '97 digital controller. Wherever possible, it has pointers to additional considerations for supporting future proliferation or derivatives of the ICH5 digital controller. However, considerations for these future devices are subject to change.

# 2.1 Intel<sup>®</sup> ICH5 AC '97 Controller Compatibility

The ICH5 AC '97 controller is fully compatible with the features found in the ICH1/2/3/4 versions. This allows for current drivers developed by ISVs and IHVs to work without modifications. The ICH5 however, provides capabilities not found in ICH family components prior to ICH4. The following matrix provides a description of the available features for each of the ICHx component generations. This document specifically addresses features on ICH5 while maintaining the original programming model reference for new developers working directly with ICH5 and not previously exposed to the ICH component.

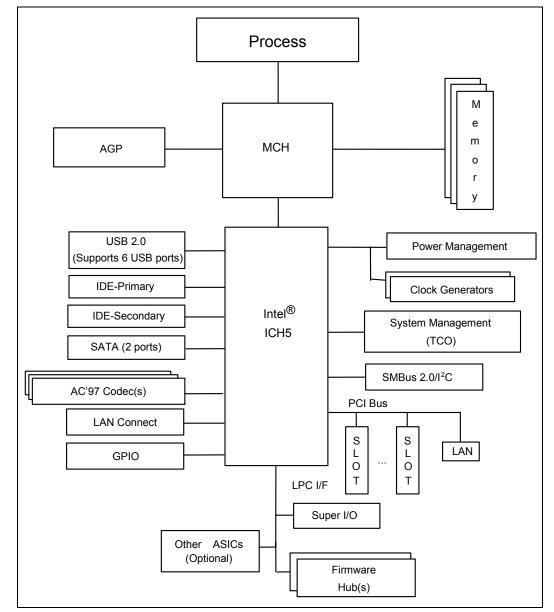

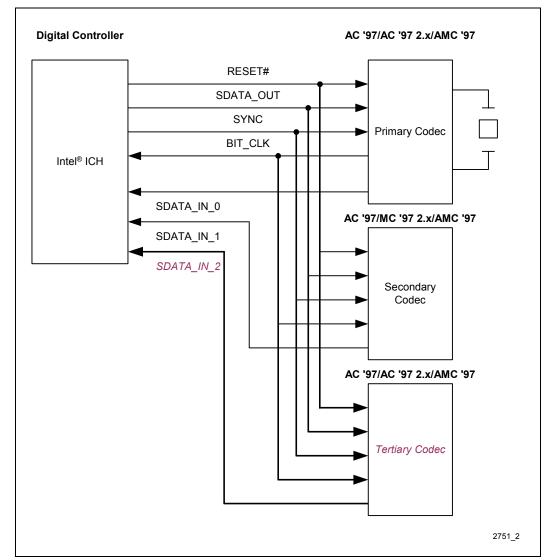

Figure 1 displays a block diagram of the platform chipset with the ICH5 component. Figure 2 represents the typical configuration for the ICH5 AC '97 controller and companion codecs.

| AC '97 Audio Controller Features      | Intel <sup>®</sup><br>ICH | Intel <sup>®</sup><br>ICH2 | Intel <sup>®</sup><br>ICH3 | Intel <sup>®</sup><br>ICH4 | Intel <sup>®</sup><br>ICH5 |

|---------------------------------------|---------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| 16 bits Stereo PCM Output             | X                         | X                          | X                          | X                          | X                          |

| 16 bits Stereo PCM Input              | X                         | X                          | X                          | X                          | X                          |

| 16 bits Microphone Input              | X                         | X                          | X                          | X                          | X                          |

| GPIO and Interrupt Support            | X                         | X                          | X                          | X                          | X                          |

| Two 2.1/2.2/2.3 Codec Support         | X                         | X                          | X                          | X                          | X                          |

| 16 bits 2/4/6 Ch. Surround PCM Output |                           | X                          | X                          | X                          | X                          |

| 20 bits 2/4/6 Ch. Surround PCM Output |                           |                            |                            | X                          | X                          |

| Dedicated S/P DIF DMA Output Ch.      |                           |                            |                            | X                          | X                          |

| Third 2.1/2.2/ 2.3 Codec Support      |                           |                            |                            | X                          | X                          |

| Memory Map Control and Status         |                           |                            |                            | X                          | X                          |

| Second 16 bits Stereo PCM Input       |                           |                            |                            | X                          | X                          |

| Second 16 bits Microphone Input       |                           |                            |                            | X                          | X                          |

| PCI 2.3 Power Management              |                           |                            |                            | X                          | X                          |

#### **Table 2. Audio Features Distribution Matrix**

The ICH5 AC '97 audio controller provides a set of features that require significant software support. The following paragraphs provide a summary of these features.

The modem support infrastructure has not been changed in any generation of the I/O controller hub starting with the ICH.

## Figure 1. Block Diagram of Platform Chipset with Intel<sup>®</sup> ICH5 Component

#### Figure 2. Intel<sup>®</sup> ICH5 AC '97 Controller Connection to Its Companion Codecs

#### 2.1.1 Third AC '97 Component Specification Revision 2.1, Revision 2.2 and Revision 2.3 Compliant Codecs

The *AC '97 Component Specification* provides capability for up to four, SDATA\_IN signals in support of up to four codecs. The ICH5 AC '97 controller provides support for up to three codecs to allow for Audio channel expansion without sacrificing the Modem Codec (MC) support. Also, the third codec capability enables a better mobile docking infrastructure.

## 2.1.2 Dedicated S/P DIF DMA Output Channel

The ICH5 controller provides a dedicated DMA engine with the capability of outputting either PCM or AC-3 data to the S/P DIF link for pass-through to an external CE audio decoder. This capability allows for simultaneous output of PCM/AC-3 on the S/P DIF link while PCM data is output to the PCM Out DMA engine. As a result, an AC3 stream from DVD movie playback can be output on the S/P DIF link concurrently with other system audio data (e.g., voice audio from a telephony application).

### 2.1.3 20 Bits Surround PCM Output

The *AC '97 Component Specification* provides a maximum bit resolution of 20 bits per sample. The ICH5 AC '97 controller PCM Output DMA Engine fully exploits this capability to improve the audio output quality.

## 2.1.4 Memory Map Status and Control Registers

The ICH5 support PCI Memory Base Address Register that allows for higher performance access to the controller registers while expanding the register space to access the third codec support mechanism. All features can now be accessed via this Memory BAR making the I/O BAR capabilities obsolete. However, the ICH5 controller may maintain the I/O BAR capability to allow for the reuse of legacy code maintaining backward compatibility to deployed driver binaries.

*Note:* This document describes the programming interface using the Memory BAR registers unless otherwise indicated. The default configuration for ICH5 Audio function is to use the PCI Memory Base Address Register. The I/O BAR is therefore disabled unless system BIOS enables the simultaneous backward-compatible capability on the register:

|        | Device 31 Function 5 Audio |         |                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|--------|----------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Offset | Register                   | Default | Comments                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 41h    | CFG<br>Configuration       | 00h     | When cleared, the I/O space BARs at offset 10h and 14h become read only registers. This is the default state for the I/O BARs. Initialized by BIOS when backward I/O Bar compatibility is required Memory BARs are always enabled. |  |  |  |  |  |  |

### 2.1.5 Second Independent Input DMA Engines

The ICH5 continues to provide two sets of input DMA engines that allow for the secondary or tertiary codecs to provide recording PCM data streams on the primary codec while simultaneously providing recording capabilities from the secondary or tertiary codec. A typical application is to provide independent input stream in a mobile docking configuration where an audio codec is located in the base system (notebook unit) and the secondary or tertiary codec is located in a docking unit for desktop replacement. The DMA engines provide the infrastructure for s/w to select the input stream from either source for stereo or microphone recording. Also the capability of simultaneous input streams opens the possibilities for more futuristic applications where a multiple microphone array can be created using two codecs. Refer to Section 3.2 for more information on how to program the DMA engines.

### 2.1.6 PCI Local Bus Specification, Revision 2.3 Power Management

The ICH5 provides *PCI Local Bus Specification*, Revision 2.3-compliant power management registers that allows for better OS power management support with reduced overhead to the BIOS programmers using ACPI control methodologies.

## 2.2 General Requirements

It is assumed that the reader has a working knowledge of AC '97 architecture and the ICH5 AC'97 controller implementation. Also, the reader should have an understanding of audio driver development for the target operating systems.

This document outlines the software specification for the AC '97 digital controller, and also includes details necessary for development of an audio device driver.

# 3 Intel<sup>®</sup> ICH5 AC '97 Controller Theory of Operation

The ICH5 AC '97 digital controller (DC) interface is an implementation of the AC-link, with additional features to support the transaction and device power management. The ICH5 AC'97 DC includes DMA engines for high-performance data transfer to memory via a hub interface.

ICH5 AC'97 DC and AC-link support isochronous traffic, which emphasizes the timing of the data. This is critical to maintain the data stream from the audio and/or modem codec.

# 3.1 Intel<sup>®</sup> ICH5 AC '97 Initialization

### 3.1.1 System Reset

The ICH5 AC '97 circuitry is reset on power up by combining the PCIRST# signal with the AC Link RESET# signal. However, AC Link RESET# will not follow PCIRST# during a resume from sleep condition. During operation, the system can be reset by clearing the AC '97 cold reset bit in the Global Control/Status register (GLOB\_CNT). This bit is maintained during ICH5 sleep mode and can be used by the driver to select warm or cold reset during a resume condition. At least one codec must be present. Otherwise, ICH5 AC '97 is not supported and the codec ready will never be seen by the controller. Once the reset has occurred, a **read** to Mixer register 00h/80h will indicate what type of hardware resides in the codec(s).

Software must ensure that the codec ready bit is present for the appropriate Global Control/Status register (GLOB\_CNT). Before writing any value on the codec registers or initiating a DMA transfer, s/w must ensure that the codec has reached a ready status by reading the Audio codec register Powerdown Control/Status register (Index 26h) or Extended Modem Status and Control register (Index 3Eh) correspondingly.

### 3.1.2 Codec Topology

The following rules present the allowable codec configuration when attaching to the AC-link interface. To avoid improper driver loading, the system BIOS should determine the presence of the audio or modem codec attached on the AC-link, and enable the Audio or Modem function's PCI configuration space accordingly.

#### The following are the loading rules for ICH5:

- 1. Maximum of three codecs total on the link

- 2. Maximum of a single modem function, either as Modem Codec or a combination Audio/Modem Codec

This information is used to disable (hide) the appropriate PCI function. To determine that a codec or codecs are attached to the link, the System BIOS follows an algorithmic approach.

Drivers can distribute output and input data in appropriate slots associated with available codec(s). For example a 6-channel data stream can be separated into three, 2-channel codec streams as long as the codecs are programmed to decode the appropriate slot output stream (SDATA\_OUT). Similarly ICH5 provides two stereo PCM input channels as well as two microphone mono input DMA channels. These allow for separate input streams for stereo PCM and microphone recording from two different codecs simultaneously.

Software should match sample rates, when two codecs are teamed together. The codecs must have matching vendors, types, and be explicitly supported in software. Essentially, audio codecs must be programmed with a common sample rate. The selection of a common sample rate is based on each codec's capabilities, as detailed in Section 3.5.3.

## 3.1.3 BIOS PCI Configuration

The ICH5 AC '97 controller, as previously indicated, exposes two PCI functions in the ICH5 (Bus 0, Device 31h). This allows for driver differentiation between these capabilities in the component.

- Function 5: ICH5 AC '97 audio controller

- Function 6: ICH5 AC '97 modem controller

As PCI devices there are a number of registers that are required to be initialized to enable these functions. The following table summarizes these requirements.

|           | Device 31 Function 5 Audio                              |           |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-----------|---------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Offset    | Register                                                | Default   | Comments                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 04h-05h   | Command (COM)                                           | 0000h     | Bit 2: Bus Master Enable<br>Bit 1: Memory Space Enable<br>Bit 0: When enable in 41h I/O Space Enable                                                                                                                                 |  |  |  |  |  |  |

| 10h-13h   | Native Audio Mixer Base<br>Address (NAMBAR)             | 00000001h | When enable in 41h Address in the 64- K I/O space that allows 256 bytes of registers not in conflict with any other set                                                                                                              |  |  |  |  |  |  |

| 14h - 17h | Native Audio Bus<br>Mastering Base Address<br>(NABMBAR) | 00000001h | When enable in 41h Address in the 64-K I/O space that allows 256 bytes of registers not in conflict with any other set                                                                                                               |  |  |  |  |  |  |

| 18h – 1Bh | Memory Audio Mixer<br>Base Address (MMBAR)              | 00000000h | Address in the 4-GB memory space that allows 512 bytes of registers not in conflict with any other set                                                                                                                               |  |  |  |  |  |  |

| 1Ch – 1Fh | Memory Bus Master<br>Base Address Register<br>(MBBAR)   | 00000000h | Address in the 4-GB memory space that allows 512 bytes of registers not in conflict with any other set                                                                                                                               |  |  |  |  |  |  |

| 3Ch       | Interrupt Line (INTLN)                                  | 00h       | A hardware interrupt (0-Fh) that follows value assigned to PIRQB#.<br>Has not effect on ICH5 it is used to indicate software the IRQ value<br>assigned to the device.                                                                |  |  |  |  |  |  |

| 41h       | CFG Configuration                                       | 00h       | When cleared, the I/O space BARs at offset 10h and 14h become read only registers. This is the default state for the I/O BARs.<br>Initialize by BIOS when backward I/O Bar compatibility is required Memory BARs are always enabled. |  |  |  |  |  |  |

#### Table 3. Audio Registers

#### Table 4. Modem Registers

|           | Device 31 Function 6 Modem                           |           |                                                                                                                                                                       |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Offset    | Register                                             | Default   | Comments                                                                                                                                                              |  |  |  |  |  |  |  |

| 04h-05h   | Command (COM)                                        | 0000h     | Bit 2: Bus Master Enable<br>Bit 0: I/O Space Enable                                                                                                                   |  |  |  |  |  |  |  |

| 10h-13h   | Native Audio Mixer Base<br>Address                   | 00000001h | Address in the 64-K I/O space that allows 256 bytes of registers not in conflict with any other set                                                                   |  |  |  |  |  |  |  |

| 14h - 17h | Native Audio Bus<br>Mastering Base Address<br>(MBAR) | 00000001h | Address in the 64-K I/O space that allows 256 bytes of registers not in conflict with any other set                                                                   |  |  |  |  |  |  |  |

| 3Ch       | Interrupt Line (INTLN)                               | 00h       | A hardware interrupt (0-Fh) that follows value assigned to PIRQB#.<br>Has not effect on ICH5 it is used to indicate software the IRQ value<br>assigned to the device. |  |  |  |  |  |  |  |

With the exception of register 41h on Device 31 Function 5, initialization of the PCI registers above is the responsibility of the PnP capable OS. If a PnP OS is not available in the system, it is then the BIOS's responsibility to configure all PCI devices including the registers above. Determination of the presence of PnP capable OS is usually made via a switch in the System Setup. However, the final configuration or the existence or not of this switch is implementation dependent.

The ICH5 AC'97 controllers also provide PCI Power Management functionality. PCI Power Management Registers are available via the configuration space. Handling of the Power Management registers is responsibility of the OS PCI Bus driver following standard procedures. For further discussion on the usage model for this registers, refer to Section 3.6, Power Management.

## 3.1.4 Hardware Interrupt Routing

The audio and modem functions in the ICH5 internally share the same PCI IRQ (PIRQB#). The configuration software must take this into account and assign the same IRQ pin to both functions. Sharing IRQs increases the ISR latencies. Each ISR must determine if the interrupting device is the one serviced by the routine, as determined by the OS programming model. PIRQB# it is also exposed as a PCI IRQ.

In an environment where a high Quality of Service (QoS) is required, system designers must pay close attention to devices attached to the same PIRQ. Software driven signal processing functions, as in the case of software driven modem and audio, require maintaining a low latency interrupt service in order to maintain proper functionality. Software driver programmers need to pay close attention to the ISR latencies and make use of Deferred Procedure Calls (DPC) as much as possible.

## 3.1.5 PCI Lock

Note that host controllers are not required to support exclusive-access mechanisms (such as PCI LOCK) for accesses to the memory-mapped register space. Therefore, if software attempts exclusive-access mechanisms to the AC '97 host controller memory-mapped register space, the results are undefined.

## 3.2 DMA Engines

The ICH5 AC '97 controller uses a scatter gather mechanism to access memory. There are five, 16-bit DMA engines for Audio: 2 PCM Stereo In, 2 MIC mono in, and S/P DIF Out. There is one, 20-bit PCM 2/4/6 channel surround DMA engine. There are two, 16-bit DMA engines for Modem: In and Out. Audio and Modem registers are located in two separate PCI functions in the ICH5 components to allow for driver development flexibility.

### 3.2.1 Buffer Descriptor List

The Buffer Descriptor List (BDL) allows device drivers to program DMA transfer using the ICH5 controller. The BDL is an array of up to 32 entries, each of which describes a data buffer. Each entry contains a pointer to a data buffer, control bits and the length expressed as the number of samples contained in the data buffer. The buffer length is restricted to 65535 samples. Samples can be either 16 or 20 bits. Refer to section 3.4.1, for more details on the layout of samples in the data buffer. A value of "0" in the buffer length indicates **no samples** to process. Each descriptor can point to a buffer of a different size.

#### Figure 3. Generic Form of Buffer Descriptor (One Entry in the List)

| (Dword 0 :-03h | ו)<br>31  |     |           |       | 1             | 0 |

|----------------|-----------|-----|-----------|-------|---------------|---|

|                |           |     | Buffer Po | inter |               | 0 |

| (Dword 1 :-07h | ו)        |     |           |       |               |   |

|                | <u>31</u> | 30  | 16        | 15    |               | 0 |

|                | IOC       | BUP | R         |       | Buffer Length |   |

|                |           |     |           |       |               |   |

#### Table 5. BD Buffer Pointer (DWORD 0: 00-03h)

| Bit  | Description                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:1 | <b>Buffer pointer</b> . This field points to the location of the data buffer. Since the samples can be as wide as 1 word, the buffer needs to be aligned to word boundaries to avoid having samples straddle DWord boundaries. |

| 0    | Reserved. Must be 0 when writing this field.                                                                                                                                                                                   |

#### Table 6. BD Control and Length (DWORD 1: 04-07h)

| Bit   | Description                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | <b>Interrupt on Completion (IOC)</b> 1= Enable , 0 = Disable. When this it is set, it means the controller should issue an interrupt upon completion of this buffer. It should also set the IOC bit in the status register. |

| 30    | <b>Buffer Underrun Policy (BUP)</b> 0 = When this buffer is complete, if the next buffer is not yet ready, (last valid buffer has been processed) then continue to transmit the last valid sample.                          |

|       | 1 = When this buffer is complete, if this is the last valid buffer, transmit zeros after this buffer is completely processed. This bit will typically be set only if this is the last buffer in the current stream.         |

| 29:16 | Reserved. Must be 0 when writing this field.                                                                                                                                                                                |

| 15:0  | <b>Buffer length</b> . This is the length of the data buffer in number of samples. The controller uses this data to determine the length of the buffer in bytes. A value of 0 indicates <u>no sample</u> to process.        |

## 3.2.2 DMA Initialization

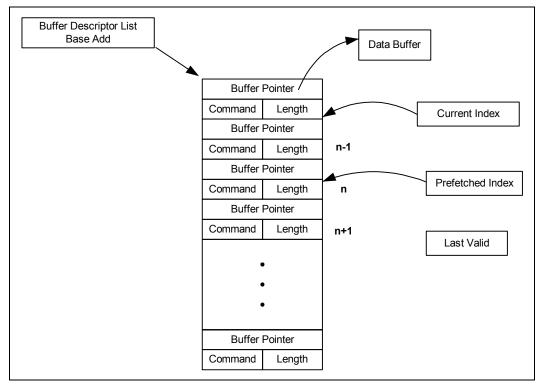

The maximum length of the buffer descriptor list is fixed at 32 (this is limited by the size of the index registers). Figure 4, below, describes the organization of the Buffer Descriptor List.

#### Figure 4. Buffer Descriptor List

The following steps describe the driver initialization process for a single DMA engine. The same process should be repeated for each DMA engine.

- 1. Create the buffer descriptor list structure in non-pageable memory.

- 2. Write the Buffer Descriptor List Base Address register with the base address of the buffer descriptor list.

#### Table 7. Audio Descriptor List Base Address

| Audio Buffer Descriptor List Base<br>Address | I/O Address:         |

|----------------------------------------------|----------------------|

| PCM IN                                       | MBBAR + 00h (PIBAR)  |

| PCM OUT                                      | MBBAR + 10h (POBAR)  |

| MIC                                          | MBBAR + 20h (MCBAR)  |

| MIC 2                                        | MBBAR + 40h (M2DBAR) |

| PCM2 IN                                      | MBBAR + 50h (PI2BAR) |

| SPDIF                                        | MBBAR + 60h (SPBAR)  |

#### Table 8. Modem Descriptor List Base Address

| Modem Buffer Descriptor List Base<br>Address | I/O Address:          |

|----------------------------------------------|-----------------------|

| Line IN                                      | MBAR + 00h (MIBDBAR)  |

| Line OUT                                     | MBAR + 10h (MOBDBAR), |

- 3. Set up the buffer descriptors and their corresponding buffers. Buffers are usually passed to the device driver as a list of descriptors that reference physical pages. These lists describe the physical page numbers associated with the pages in the virtual audio buffer. Multiple buffer descriptors may be required to represent a single virtual buffer passed to the device driver

- 4. Once buffer descriptors are set in memory, software writes the Last Valid Index (LVI) register.

#### Table 9. Audio Last Valid Index

| Audio Last Valid Index (LVI) | I/O Address:         |

|------------------------------|----------------------|

| PCM IN                       | MBBAR + 05h (PILVI), |

| PCM OUT                      | MBBAR + 15h (POLVI), |

| MIC                          | MBBAR + 25h (MCLVI)  |

| MIC 2                        | MBBAR + 45h (M2LVI)  |

| PCM2 IN                      | MBBAR + 55h (PI2LVI) |

| SPDIF                        | MBBAR + 65h (SPLVI)  |

#### Table 10. Modem Last Valid Index

| Modem Last Valid Index (LVI) | I/O Address:        |

|------------------------------|---------------------|

| Line IN                      | MBAR + 05h (MILVI)  |

| Line OUT                     | MBAR + 15h (MOLVI), |

5. After LVI registers are updated, software sets the run bit in the control register to execute the descriptor list.

## 3.2.3 DMA Steady State Operation

Software has two concurrent activities to perform while in normal operation: Preparing new buffers/buffer descriptors and marking processed buffer descriptors and buffers as free. Once the run bit is set in the bus master control register bit 0, the bus master fetches the buffer descriptor.

- 1. Bus master starts processing the current buffer. Once current buffer is processed, depending upon the bits set in the command field, the interrupt is asserted and the interrupt bit is set.

- 2. Bus master increments the current and pre-fetch indices. It then starts executing the current buffer and schedules the next buffer to be pre-fetched.

- 3. Buffer service routine maintains a variable that points to the head of the list of descriptors to be processed. The descriptor list service routine performs the following activities:

```

// Update head of descriptors to be processed

While (head != current_index)

{

Mark head free ;

// check for end of descriptor list

If head == base_address + (31 * 8);

// last entry on the list, set head to top of the list

head = base_address;

Else

// still inside the list, increment head to next entry

head++;

```

*Caution:* This algorithm needs to be optimized to reduce the number of memory accesses during execution. The "while" statement could translate to several memory access if this code is not execute after each buffer descriptor update.

Also, the routine that prepares buffers maintains a variable that points to the entry *after* the tail of the list. This value is always the next entry after the Last Valid Index register. It follows the following algorithm:

```

// Update tail of descriptor list ready for execution and audio

// buffers when available for processing

While ((tail == free) && (buffers_available > 0))

{

Prepare buffer descriptor indexed by tail;

buffers_available--;

//assign tail to Last Valid Index

LVI = Tail;

// check for end of descriptor list

If (tail == base_address + 31 * 8);

// last entry on the list, set tail to top of the list

tail = base_address;

Else

```

```

// Advance tail to next value

tail++;

```

### 3.2.4 Stopping Transfers

}

There are two ways that DMA transfers can be stopped.

- 1. By simply turning off the Bus Master run/pause bit. This will halt the current DMA transfer immediately. Data in the output FIFOs will continue to be read out until they empty. The registers will retain their current values and AC-link corresponding slots will be invalidated. Setting the run/pause bit will resume DMA activity.

- 2. Software can stop creating new buffers and hence not update the last valid index register. The bus master will stop once the last valid buffer has been processed. All register information is maintained. During this condition the controller will transmit the last valid sample or zeros pending the status of the Buffer Underrun Policy (BUP) bit in the buffer descriptor entry. If the run/pause bit remains set, then any future update to the Last Valid Index register will cause the bus master operation to resume.

# *Note:* Software must ensure that the DMA controller halted bit is set before attempting to reset registers.

### 3.2.5 FIFO Error Conditions

Two general conditions could result in the FIFO error bit 4 in the status register being set. Pending the status of bit 3 in the control register it will also cause an interrupt.

#### 3.2.5.1 FIFO Underrun

FIFO underrun will occur when the ICH5 AC '97 controller FIFO is drained:

- 1. As a result of system congestion. The DMA read transaction could still be pending as data has not returned from memory. In this case the controller will repeat last sample until new data is available in the FIFO.

- 2. As a result of DMA engine reaching the Last Valid Index, no further access to memory, therefore FIFO will drain. In this case the controller will transmit the last valid sample or zeros pending the status of the Buffer Underrun Policy (BUP) bit in the buffer descriptor entry. This condition is an error if software is not able to update the descriptor list before the DMA engine reaches the Last Valid Index. However, this condition could be as result of the completing processing the last buffer. It is up to the software driver to determine the final status of this condition. See also Stopping Transfers, Section 3.2.4.

#### 3.2.5.2 FIFO Overrun

FIFO overrun will occur when valid data is transmitted in proper AC-link slots and DMA FIFO remains full. Two conditions could result in the FIFO error bit 4 in the status register being set. Pending the status of bit 3 in the control register it will also cause an interrupt.

1. As a result of DMA engine not being able to update system memory with the content of the FIFO. This is a result of system congestion. In this case, all new samples received from the AC-link will be lost.

2. As a result of the DMA engine reaching the Last Valid Index, no further access to memory, therefore FIFO will not drain. This condition is an error if software is not able to update the descriptor list before the DMA engine reaches the Last Valid Index. However, this condition could be the natural result of the last buffer entry been processed. It is up to the software driver to determine the final status of this condition. See also Stopping Transfers in paragraph above.

# 3.3 Channel Arbitration

It is possible for up to eight ICH5 AC '97 DMA channels to be enabled at one time. A round-robin arbitration scheme is used to arbitrate between these channels.

# 3.4 Data Buffers

## 3.4.1 Memory Organization of Data

Samples are packed in an interleaved format: two samples for two channel (stereo), four samples for four channels surround and six samples for six channels surround.

The actual PCM data is "left-aligned" within the container. The sample itself is justified most significant; all extra bits are at the least-significant portion of the container. All non-valid data bits must be set to 0. With 20 bit data, the "top" 20 bits (31-12) of the DWORD contain the data. The bottom 12 bits (11-0) are not valid data. The sample data must be WORD aligned.

### 3.4.2 PCM Buffer Restrictions

Below are the memory buffer restrictions for ICH5 PCM that applies for 2-, 4-, and 6-channel audio mode:

1. Buffer Descriptors Must Contain Integer Multiples of Framed Samples and Are Frame Aligned:

Example: Two channel buffers must contain an integer multiple of two samples. Four channel buffers must contain a multiple of four samples and six channel buffers must contain a multiple of six samples. The controller does not support a frame (e.g., left and right samples for two channel) spanning multiple descriptors. Similarly, the controller does not support a buffer descriptor with a single sample (PCM out MONO is not supported). Also, odd length buffers are not allowed due to the sample alignment requirements.

2. Software Is Allowed to Create an Empty Frame (0 Samples) in a Buffer Descriptor with the Following Restriction:

An empty buffer has to be part of a list of buffer descriptors and it cannot to be the first Buffer Descriptor or the last Buffer Descriptor of the list. A series of buffer descriptors with 0 samples are possible in the lists as long as they are not the first or the last. The last Buffer Descriptor in the list is determined by the last valid index (LVI) that is programmed.

### 3.4.3 FIFO Organization

The ICH5 AC '97 controller supports 16-bit samples on all channels except PCM Out, which also supports 20-bit samples.

Data will be written to the FIFO in sample pairs following the order of valid slots in a channel. For example, for audio PCM In, the controller will check the first valid slot and add it to the FIFO first entry as a word (16 bits). The next valid slot will be added as the second word entry in the FIFO to create the PCM stereo sample pair. This behavior works under the assumption that the first valid slot will be always the Left channel (slot 3) followed by Right channel in slot 4 in the same or subsequent frame. If the codec transmits data repeating the slot, it will cause the controller to misplace the sample in the FIFO. Codecs compatible with the ICH5 AC '97 implementation should always maintain the indicated order, and never use the same slot twice to transmit samples to the controller. The figures below present some ICH5 compatible and incompatible implementations using as a reference a two-channel implementation.

#### Figure 5. Compatible Implementation with Left and Right Sample Pair in Slot 3/4 Every Frame

| Slot #      | 0   | 1             | 2              | 3 | 4 | 5          | 6    | 7    | 8    | 9    | 10   | 11   | 12             |

|-------------|-----|---------------|----------------|---|---|------------|------|------|------|------|------|------|----------------|

| SYNC _      |     |               |                |   |   |            |      |      |      |      |      |      |                |

| Frame n     | TAG | CMD<br>ADR    | CMD<br>DATA    | x | x | MDM<br>CDC | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Control |

|             | TAG | Status<br>ADR | Status<br>Data | x | x | MDM<br>CDC | MIC  | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Status  |

| -rame n + 2 | TAG | CMD<br>ADR    | CMD<br>Data    | x | x | MDM<br>CDC | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Control |

| Frame n + 3 | TAG | Status<br>ADR | Status<br>Data | x | x | MDM<br>CDC | MIC  | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Status  |

# Figure 6. Compatible Implementation with Sample Rate Conversion Slots 3 and 4 Alternating over Next Frame

| Slot #     | 0   | 1             | 2              | 3 | 4 | 5          | 6    | 7    | 8    | 9    | 10   | 11   | 12             |

|------------|-----|---------------|----------------|---|---|------------|------|------|------|------|------|------|----------------|

| SYNC       |     |               |                |   |   |            |      |      |      |      |      |      |                |

| Frame n    | TAG | CMD<br>ADR    | CMD<br>DATA    | x |   | MDM<br>CDC | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Control |

|            | TAG | Status<br>ADR | Status<br>Data |   | x | MDM<br>CDC | MIC  | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Status  |

| rame n + 2 | TAG | CMD<br>ADR    | CMD<br>Data    | x |   | MDM<br>CDC | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Control |

| rame n + 3 | TAG | Status<br>ADR | Status<br>Data |   | x | MDM<br>CDC | MIC  | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Status  |

#### Figure 7. Incompatible Implementation of Sample Rate Conversion with Repeating Slots over Next Frames

| Slot #      | 0   | 1             | 2              | 3 | 4 | 5          | 6    | 7    | 8    | 9    | 10   | 11   | 12             |

|-------------|-----|---------------|----------------|---|---|------------|------|------|------|------|------|------|----------------|

| SYNC        |     |               |                |   |   |            |      |      |      |      |      |      |                |

| Frame n     | TAG | CMD<br>ADR    | CMD<br>DATA    | x |   | MDM<br>CDC | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Control |

| Frame n + 1 | TAG | Status<br>ADR | Status<br>Data |   | x | MDM<br>CDC | MIC  | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Status  |

| Frame n + 2 | TAG | CMD<br>ADR    | CMD<br>Data    |   | x | MDM<br>CDC | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Control |

| Frame n + 3 | TAG | Status<br>ADR | Status<br>Data | x |   | MDM<br>CDC | MIC  | RSVD | RSVD | RSVD | RSVD | RSVD | I/O<br>Status  |

#### Table 11. FIFO Summary

| Channel   | # of Samples | FIFO Depth | FIFO Width | Comments                               |

|-----------|--------------|------------|------------|----------------------------------------|

| Mic In    | 1            | 2          | 32 bits    | 2 frame <sup>1</sup> dword             |

| Mic2 In   | 1            | 2          | 32 bits    | 2 frame <sup>1</sup> dword             |

| PCM In    | 2            | 4          | 32 bits    | 1 frames per dword                     |

| PCM2 In   | 2            | 4          | 32 bits    | 1 frames per dword                     |

| PCM Out   | 6, 4 or 2    | 24         | 32 bits    | 1 frames per dword (2 –16 bits ch),    |

|           |              |            |            | 1 frame per 2 dword (2 –20 bits ch)    |

|           |              |            |            | 1 frame per 2 dword (4 –16 bits ch)    |

|           |              |            |            | 1 frames per 4 dword (4 –20 bits ch)   |

|           |              |            |            | 1 frames per 3 dword (6 – 16 bits ch.) |

|           |              |            |            | 1 frames per 6 dword (2 –20 bits ch)   |

| Modem In  | 1            | 2          | 32 bits    | 2 frames per dword                     |

| Modem Out | 1            | 2          | 32 bits    | 2 frames per dword                     |

#### NOTES:

1. One audio frame worth of data for the specific DMA channel.

# 3.5 Multiple Codec/Driver Support

The ICH5 AC '97 controller is capable of supporting a three-codec implementation. Under this implementation all codecs share the SDATA\_OUT signal while independent SDATA\_IN[0:2] are used by the codec to supply data to the controller. ICH5 allows for a compatible behavior, where the three SDATA\_IN are used, these signals are logically OR'd inside the digital controller, effectively creating one digital input data stream. However, ICH5 allows for an independent SDATA\_IN functionality. In this case, the SDATA\_IN Map Register (SDM) MBBAR + 80h is used to steer the content of the input slots to the appropriate controller DMA engine. This capability also allows for a more reliable enumeration algorithm of the available codecs.

#### Table 12. SDM Register Description

| Bit | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                          |

|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      |       | PCM In 2, Microphone In 2 Data In Line (D21L): When the SE bit is set, these bits indicate which SDATA_IN line should be used by the hardware for decoding the input slots for PCM In 2 and Microphone In 2. When the SE bit is cleared, the value of these bits is irrelevant, and PCM In 2 and Mic In 2 DMA engines are not available.             |

| 7:6 | RW   | 00    | 00 SDATA_IN0                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 01 SDATA_IN1                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 10 SDATA_IN2                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 11 Reserved                                                                                                                                                                                                                                                                                                                                          |

|     |      |       | PCM In 1, Microphone In 1 Data In Line (DI1L): When the SE bit is set, these bits indicates which SDATA_IN line should be used by the hardware for decoding the input slots for PCM In 1 and Microphone In 1. When the SE bit is cleared, the value of these bits are irrelevant, and the PCM In 1 and Mic In 1 engines use the OR'd SDATA_IN lines. |

| 5:4 | RW   | 00    | 00 SDATA_INO                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 01 SDATA_IN1                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 10 SDATA_IN2                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 11 Reserved                                                                                                                                                                                                                                                                                                                                          |

| 3   | RW   | 0     | Steer Enable (SE): When set, the SDATA_IN lines are treated separately and not OR'd together before being sent to the DMA engines. When cleared, the SDATA_IN lines are OR'd together, and the "Microphone In 2" and "PCM In 2" DMA engines are not available.                                                                                       |

| 2   | RO   | 0     | Reserved                                                                                                                                                                                                                                                                                                                                             |

|     |      |       | Last Codec Read Data Input (LDI): When a codec register is read, this indicates which SDATA_IN the read data returned on. Software can use this to determine how the codecs are mapped. The values are:                                                                                                                                              |

| 1:0 | RO   | 00    | 00 SDATA_INO                                                                                                                                                                                                                                                                                                                                         |

|     | -    |       | 01 SDATA_IN1                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 10 SDATA_IN2                                                                                                                                                                                                                                                                                                                                         |

|     |      |       | 11 Reserved                                                                                                                                                                                                                                                                                                                                          |

### 3.5.1 Codec Register Shadowing

Codec register reads are presented in the AC-link in the next available frame after the controller receives the I/O transaction. Data will be returned to the controller pending codec availability. To avoid longer latencies than necessary, the codec must return data in the next available frame. Multiple frame transactions impose large system latencies, to the detriment of system performance.

Even when data is returned in the frame immediately after the read request is presented in the AC-link, the minimum latency is still on the order of 40  $\mu$ s. To minimize the effect on the system caused by long latencies in the AC-link, software drivers **must** maintain a copy of the codec register in memory (shadow) and use this data instead of accessing the codec.